-

[ARMv8 기초] Exception이란? (Exception type : synchronous exception, asynchronous exception)하드웨어 스케치북 2020. 4. 5. 17:50반응형

지난 포스팅들에서 ARMv8 아키텍쳐의 기본이 되는 Exception level이라는 개념과 Exception level 변경을 위해 SPSR (Saved Program Status Register) 과 PSTATE (Processor State) 라는 개념을 알아보았다.

이번 포스팅에서는 그럼 도대체 Exception이라는게 무엇인지에 대해 알아볼 것이다.

ARMv8 Fundamental

3. Changing Exception level and security state

3-3. Exception 이란?

Exception

Excpetion이란 말 그대로 '예외'이다. 무언가 예외적인 상황이 발생하는 것.

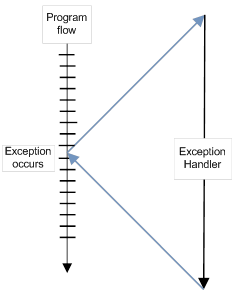

우리가 학교에서 Interrupt에 대해 배웠고, Interrupt가 발생하면 하던 일을 멈추고 Interrupt Handler로 분기하여 Interrupt service routine (ISR)을 수행하고 다시 돌아와 하던 일을 수행한다고 배웠다.

Exception도 마찬가지이다. Exception이 발생하면 Exception handler로 분기하여 Exception을 처리하고 다시 복귀하는 것이다.

그렇다면 ARMv8 architecture에서 exception을 발생시키는 것은 어떤 것이 있을까?

Exception type - Synchronous exception과 Asynchronous excpetion

Exception의 종류는 Synchronous/Asynchronous로 나뉜다. 이 것을 나누는 기준은 'Instruction'이다. 간단히 얘기하면 Instruction에 synchronous인지 아닌지에 의해 타입이 나뉜다.

-

Synchronous Exception (동기 예외)

Synchronous exception에 대해 ARM document에서는 아래와 같이 설명한다.

"An exception is described as synchronous if it is generated as a result of execution or attempted execution of the instruction stream, and where the return address provides details of the instruction that caused it"

앞서 이야기한 것처럼 특정 Instruction을 수행하려고 할 때 exception이 발생하고, 어떤 address로부터 exception이 발생했는지 명확하게 ELR을 return할 수 있는 경우를 synchronous exception이라고 한다.

Synchronous exception의 종류는 아래와 같다.

- Instruction aborts from the MMU : MMU로 mapping된 곳으로 부터의 Instruction fetch abort

-

For example, By reading an instruction from a memory location marked as Execute Never : Execute Never로 설정된 지역을 Read하는 경우

-

- Data Aborts from the MMU : 접근 불가능한 영역을 접근할 때 혹은 misaligned address를 접근할 때

-

For example, Permission failure : Non secure state에서 secure memory를 접근할 때

-

- SP and PC alignment checking : PC/SP alignment abort

-

PC가 4byte align일 때 0x0000_0002와 같이 2Byte aligned address에 access하는 경우

-

- Synchronous external aborts.

-

For example, an abort when reading translation table.

-

- Unallocated instructions

-

For example, UNDIFNED instruction : Instruction decoding에 실패한 경우 (Fetch data가 깨지는 경우)

-

- Debug exceptions : Debug access에 의해 발생하는 exception

-

Breakpoint Instruction exception, Breakpoint exception, Watchpoint exception, Vector Catch exception, Software Step exception : Debugger (e.g., Trace32) 를 사용할 때 발생하는 exception

-

- Exception generating

이처럼 Synchronous exception의 경우 원인 파악이 비교적 쉽기 때문에 해결 방법을 찾기가 간단한 편이다.

-

Asynchronous Exception (비동기 예외)

Asynchronous exception에 대해 ARM document는 아래와 같이 설명한다.

"An asynchronous exception is not generated by executing instructions, while the return address might not always provide details of what caused the exception"

이렇게 무책임한 eception이 있다니. 특정 instruction을 수행할 때 생기는 것이 아니며 무엇이 exception을 발생시켰는지 정보를 항상 제공할 수 없단다.

Asynchronous exception의 종류는 아래와 같다.

- IRQ (Interrupt Request) : Normal priority interrupt가 발생했을 때

- FIQ (Fast Interrupt Request) : IRQ에 비해 높은 priority를 가지는 Fast interrupt가 발생했을 때

- SError (System Error) :

-

System errors have a number of possible causes, the most common being asynchronous Data Aborts (for example, an abort triggered by writeback of dirty data from a cache line to external memory)

-

Memory에 접근하기 위해 address와 data를 특정 시점에 날리는 것이 아닌, cache policy에 의해 scheduling된 task가 external memory에 접근할 때 permission failure 등이 발생할 수 있음

-

이처럼 asynchronous exception은 명확히 어떤 동작이 exception을 발생시켰는지 찾기 어렵다. (특히 SError) System에 대한 이해가 충분히 있는 사람이 보아야 원인을 찾기 빠르다.

Exception Priority

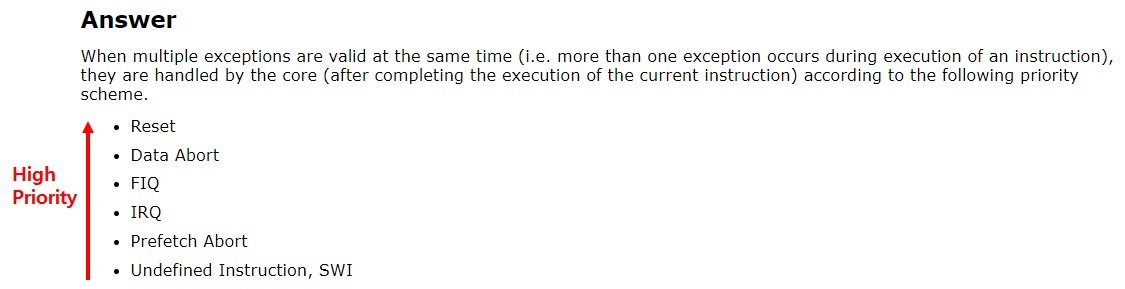

이렇게 exception 종류가 다양한데, 이 exception이 동시에 일어난다면 어떻게 될까?

ARM에서는 exception 사이에 priority, 즉 우선권이 존재한다고 설명하고 있다.

Reset이 모든 exception에 대해 우선하는 priority를 가진다. 제 아무리 system에서 지지고 볶고 해도 board에서 reset 버튼 누르면 끝이기 때문이다. 그 다음으로 Data abort, FIQ, IRQ, Prefetch Abort, UNDEFINED instruction = SWI 순서로 priority를 가진다.

그래서 보통 code를 작성할 때 0번지에서 실행되는 가장 최초의 code를 Reset entry 라고도 하는 이유가 바로 이 때문이다. Reset이 수행되면 내부적으로 Pipeline, cache flush 등의 작업을 거친 후 RVBAR_ELn (Reset Vector Base Address) 에 지정된 주소로 돌아간다.

이번 포스팅에서는 Exception의 type과 종류에 대해서 알아보았다.

Exception Vector와 Exception Handler에 관한 내용도 작성하려고 했으나 글이 길어져 다음 포스팅에 마저 작성하도록 해야 겠다.

다루어야 할 양이 많다는 것은 그만큼 Exception이 ARMv8 architecture에서 굉장히 중요한 역할을 한다는 것의 방증 아닐까? CPU Hardware를 검증하는 사람도, S/W 개발자도 모두 잘 알아두어야 하는 내용이니 만큼 꼼꼼하게 작성하고 싶다.

+ 잘못된 정보나 질문이 있다면 댓글로 남겨주세요.

반응형'하드웨어 스케치북' 카테고리의 다른 글

-